# 32kHz Design for Low Power Applications

# Reducing Power Consumption for 32kHz Quartz Crystal Oscillator Circuit

#### **Abstract**

The intent of this investigation is to show the advantages of 32kHz crystals with reduced  $C_L$  and lower ESR over conventional 32kHz crystals with regard to power consumption, oscillation allowance, starting time and drive level.

The following draft confirms the advantage of the use of Geyer Electronic KX-327NHT with Load Capacitance of 7pF instead of 12,5pF.

Part number 12.87153 7pF +/-20ppm  $\leq$  80k Ohm, 50k Ohm typ. Part number 12.87148 7pF +/-20ppm  $\leq$  50k Ohm, 35k Ohm typ.

- Considerably reduced Power Consumption

- Improved Start up Performance

- Faster Start up time

- Stable operation for lower drive level

- 1. Reducing Power Consumption in CMOS Oscillator Circuit

- 2. Relationship for CL and Power Consumption in the Oscillator Circuit

- 3. Relationship of Negative Resistance (Oscillation Allowance) and C<sub>L</sub>

- 4. Relationship for Oscillator circuit current and R<sub>1</sub>

- 5. Another Advantage of Low-C<sub>L</sub> (Oscillation Rising Time)

- 6. Another Advantage of Low-C<sub>L</sub> (Drive Level)

- 7. Precision vs. Power Consumption

Annex: Circuit Matching Investigation

#### 1. Reducing Power Consumption in CMOS Oscillator Circuit

Current consumption of the crystal oscillator circuit depend on power supply voltage ( $V_{DD}$ ), frequency, load capacitance, and  $R_1$  of the quartz crystal.

- \* Current consumption in the oscillator circuit

- 1. Charge and discharge current of  $C_L$  » Low  $C_L$

- 2. Flow-through current » Low  $R_1$

- \* Low- $C_L$  and Low- $R_1$  of the quartz crystal realizes reduction of power consumption in the oscillator circuit

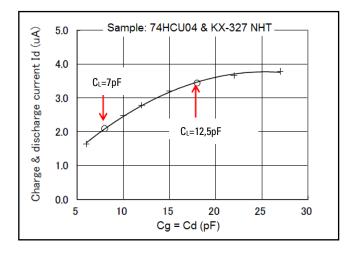

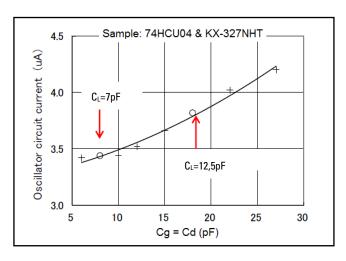

# 2. Relationship for C<sub>L</sub> and Power Consumption in the Oscillator Circuit

Charge and Discharge Current ID (Calculation)

Oscillator circuit current (Actual measurement)

$$Id = \frac{Vd}{1/(2\pi f)C_d} = (2\pi f)VdC_d$$

- \* Charge and discharge current for C<sub>L</sub>=7pF is 40% lower than for of 12,5pF.

- \* Actual measurement includes the flow-through current of the oscillation inverter. Therefore, when the flow-through current is controlled, the calculated values Approximate the actual reduction of the current consumption.

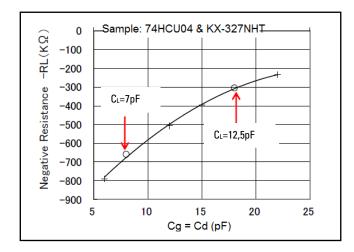

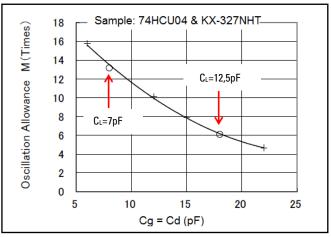

# 3. Relationship of Negative Resistance (Oscillation Allowance) and $C_L$

Negative Resistance  $-R_L$  (K $\Omega$ )

Oscillation Allowance M (Times)

$$-R_L = \frac{-g_m}{(2\pi f)^2 C_g C_d}$$

Reduction of gm and Vdd lowers the IC's power consumption, which reduces the oscillation allowance. The Crystal's low  $-C_L$  offsets the reduction of oscillation allowance.

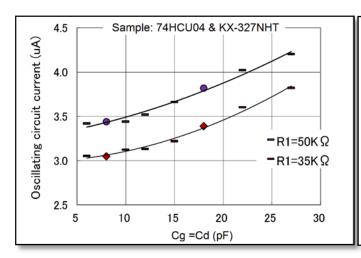

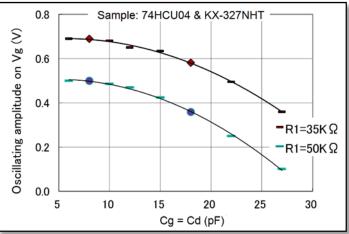

### 4. Relationship for Oscillator circuit current and R<sub>1</sub>

Oscillator circuit current (Actual measurement)

Oscillator amplitude on  $C_g$  (V)

- \* The current consumption of an oscillator circuit using 74HCU04 can decrease by Approximately 10% based on the quartz crystal motional resistance R<sub>1</sub>.

- \* Quartz crystal motional resistance  $R_1$  will be higher, the oscillator amplitude on  $C_g$  will be lower, and the flow-through current of oscillator will be higher.

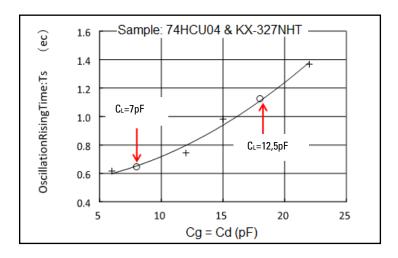

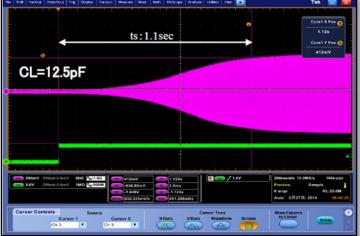

# 5. Another Advantage of Low-C<sub>L</sub> (Oscillation Rising Time)

Low CL makes a higher negative resistance. The oscillator rising time will be shorter if the  $C_L$  is lower.

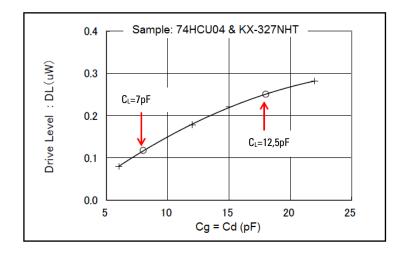

# 6. Another Advantage of Low-CL (Drive Level)

$$D_L = I^2 \ x \ R_e$$

$$\begin{split} I &= V_{\text{g}} / \left( 1 / \omega C \right) \\ R_{\text{e}} &= R_{\text{1}} \, x \, \left( 1 + C_{\text{o}} / C_{\text{L}} \right)^2 \end{split} \label{eq:eq:Relation}$$

Lower  $C_L$  reduces the quartz crystal excitation current and reduced the drive level. Excessive drive level makes the characteristics of the tuning fork quartz crystal unstable.

#### 7. Precision vs. Power Consumption

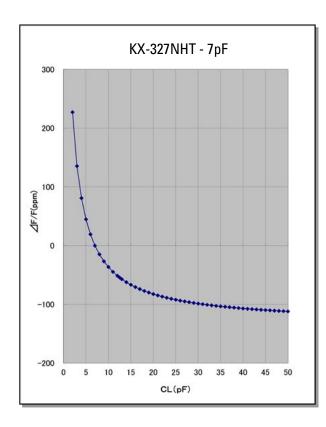

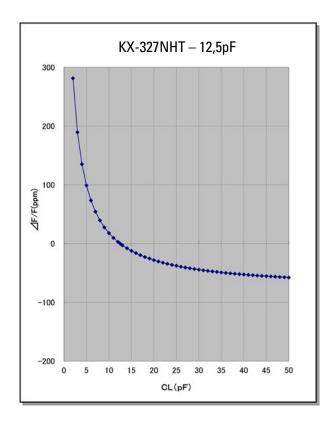

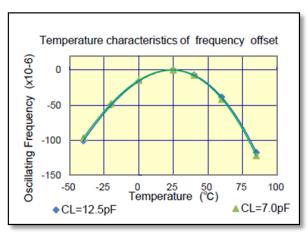

While a crystal with a low load capacitance of  $C_L = 7pF$  provides a design with low power consumption, a crystal with a higher load capacitance of  $C_L = 12,5pF$  is more advantageous for applications requiring higher precision.

As you can see from the diagram, the slope at  $C_L = 7pF$  is steeper than that at  $C_L = 12,5pF$ . This means that circuit tolerances have stronger influence on a 7pF-crystal than on a 12,5pF-crystal.

Therefore it is necessary to balance power consumption with precision.

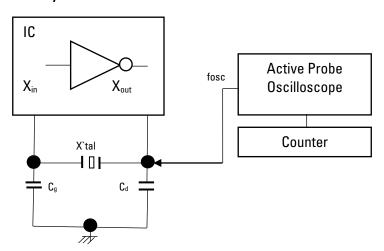

# **Annex: Circuit Matching Investigation**

#### **Result of Matching Investigation**

This is an example of our matching investigation for customers.

#### Our Crystal: KX-327NHT

Table 1. Constants

|                                       | A                     | В                  |      |                                                   |

|---------------------------------------|-----------------------|--------------------|------|---------------------------------------------------|

| Key specifications                    | C <sub>L</sub> 12,5pF | C <sub>L</sub> 7pF | Unit | Remarks                                           |

| V <sub>DD</sub> : V                   | 3,3                   | 3,3                |      |                                                   |

| Capacitance at Input: C <sub>g</sub>  | 20                    | 6                  | pF   | Optimal capacitance in response to C <sub>L</sub> |

| Capacitance at Output: C <sub>d</sub> | 20                    | 6                  | pF   |                                                   |

Table 2. Characteristic data

| Item                                     | C <sub>L</sub> 12,5pF | C <sub>L</sub> 7pF | Unit              | Remarks                                                   |

|------------------------------------------|-----------------------|--------------------|-------------------|-----------------------------------------------------------|

| Matching accurancy: f/F <sub>o</sub>     | 2,50                  |                    | x <sup>10-6</sup> | Frequency offset at specified V <sub>DD</sub>             |

| Voltage Fluctuation: +/-df/V             | -                     | 0,00               | x10 <sup>-6</sup> | V <sub>DD</sub> +/-10% (Standard operating voltage range) |

| Drive Level: D <sub>L</sub>              | 0,01                  | 0,01               | μW                | $D_L=Ix2 R_e < 1x10-6W, R_e=R_1 (1+C_o/C_L)2$             |

| Negative Resistance: I −R <sub>L</sub> I | -665                  | -1063              | k0hm              | 5 times larger than R <sub>1</sub> MAX Judgemental        |

| Oscillation Allowance: M                 | 9,5                   | 15,2               | Times             | standard of oscillation stability                         |

| Oscillation Starting Voltage             | -                     | 1,43               | V                 |                                                           |

| Oscillation Stopping Voltage             | -                     | 1,36               | V                 |                                                           |

GEYER Electronic GmbH Behringstraße 6 D-82152 Planegg/ München +49 89 546868-0